用集成电路芯片已使计算机进一步微型化和高速化日趋困难,约瑟夫逊结器件却使人们看到未来的曙光。80年代约瑟夫逊结器件的研究曾风行一时,不过由于制作稳定结电极的工艺不过关,研究结果令人失望。最近,日本工作者另辟新径,攻克了这一难题,约瑟夫逊效应计算枓的研究又重新活跃起来。

集成电路(IC)技术的持续发展,带来了信息处理机器如小型个人计算机、工作站和微型、大型计算机等的迅速普及。微型化,即减少装配在IC芯片上成分的尺寸,是重要技术之一。在刚刚过去的几十年里,它标志着半导体技术的水平。然而,在IC芯片的尺寸越来越小,直至小到毫米以下的将来,半导体技术会遇到一些棘手的问题。其中之一是发热问题:芯片上密密麻麻的晶体管由于功耗而产生热量。这是非常令人头疼的。它限制了在一块芯片上能组装晶体管的密度和数量。约瑟夫逊结器件是用超导体制成的,它的功耗只相当于半导体晶体管的千分之一,利用这一性质,可以解决发热问题。

本文下面综述举世瞩目的超高速超导计算机的开发技术,在这项技术中逻辑和存贮电路是由约瑟夫逊器件制作的。

开发约瑟夫逊计算机的原因

科学和工程计算的各领域对计算能力的要求变得越来越高,像天气预报、核聚变研究、语音识别、图像理解、卫星大地勘测等领域就是这样。为此,超级计算机,即专用于高速工作的计算机,就得到了开发和广泛应用。计算机电路中所有传播信号都由一只内部时钟保持周期同步,这只时钟有一周期时间,可用来量度计算机的处理速度。现代大型半导体计算机的周期时间大约是10毫微秒。周期时间由开关器件的开关时间和电路中电信号的传播延迟时间决定。大型计算机的信号传播延迟时间占整个周期时间的⑽%。即使使用了理想的器件,忽略不计它的开关时间,计算机系统的速度也只能提高一倍左右。信号传播的延迟时间受光速限制。当前计算机的主机体积差不多1米3,电路中的光速约是真空中的1/3。若电信号以光速穿过1米长的通路,考虑其传播的延迟时间,就可确定出机器的周期时间约是10毫微秒。若希望超级计算机快10倍,则计算机主机的物理尺寸必须减少到10厘米3。然而,工作时开关器件有功耗,若用半导体制作超级计算机,逻辑和存贮电路的1千万至1亿个晶体管就会放出大量的热量,这么小的计算机就会像个燃烧的火炉。约瑟夫逊结器件具有超高速的运算速度,功耗又极低,因而可以制作出体积极小的约瑟夫逊计算机。从70年代开始,人们对这类计算机的开发就抱有浓厚的兴趣。

历 史

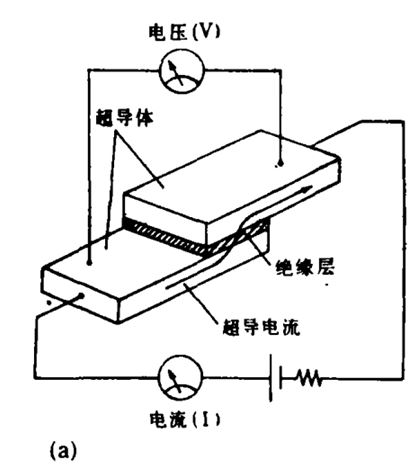

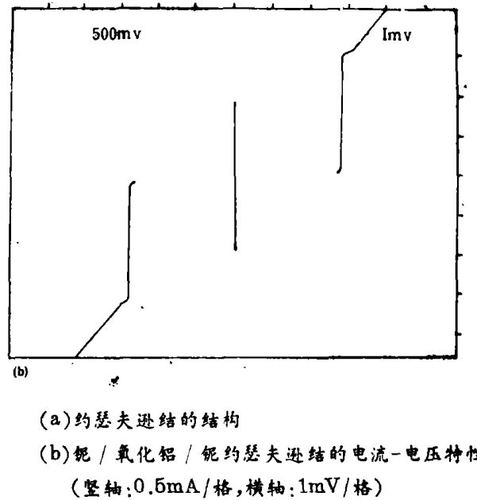

1962年剑桥大学的B. O. 约瑟夫逊从理论上指出,超导电子偶可穿过两个超导电极夹着的薄薄的绝缘屏障。第二年贝尔电话实验室的P. W. 安德森和J. W. 罗厄尔做实验证实了该效应。两层超导体电极夹着一层薄薄的绝缘层就构成了三明治结构。超导电子偶可穿越三明治结构的绝缘层,形成隧道,这就是所谓的约瑟夫逊隧道结。图1(a)所示的是两层铌超导体夹着一层足够薄的氧化物绝缘材料构成的约瑟夫逊结。宏观波方程既可描述超导状态,也可说明氧化绝缘层的渗透现象。渗透氧化物的过程中形成了电子偶隧道,并且在无任何加载电压的情况下约瑟夫逊结中就流有超导电流。若超导电流超过某一阈值,结上就有了电压。当电流是电流阈值(即临界电流)时,电压会从0迁跃到一正电压。这一特性可以用来开发逻辑电路。1966年IBM公司的J. 马帝苏依此实现了一个开关时间在亚毫微秒级上的逻辑电路。由于可和半导体器件相媲美,当时是非常引人注目的。人们看到初步成果的希望和前景后,开展了进一步的工作。IBM公司的W. 安那科提出了使用约瑟夫逊器件组装逻辑和存贮电路的超高速计算机的方案。随后,IBM公司的约瑟夫逊计算机技术的研究项目上马了。经过积极努力,IBM已可在一个芯片上集成多个约瑟夫逊结,并开发了在铅、铟和金的合金上制作约瑟夫逊结的工艺。这种铅合金制作的逻辑和存贮电路,在性能上是绝无仅有的,引起了人们特别的关注。1980年前后,集中细致的约瑟夫逊计算机技术的研究工作在其它研究所也纷纷上马了。

约瑟夫逊存贮器

IBM在终止约瑟夫逊计算机研究项目之前,做了一个约瑟夫逊信号处理机的样品以进行实验。该样品模拟了设计的处理机中可能的最长通路,丼已包含了约瑟夫逊计算机的关键部件,如逻辑电路,功率分配及综合部件。它的工作周期已能成功地降至3.7×10-9秒。然而,实验中存贮器芯片是用简陋的延迟线替代的,因为当时约瑟夫逊存贮器的工作性能不是很好。约瑟夫逊存贮器是至关重要的,甚至有人称这是IBM终止其研究项目的主要原因之一。

约瑟夫逊计算机要想存贮数据,约瑟夫逊RAM存贮器是关键。由于约瑟夫逊结的特性,约瑟夫逊RAM的存取时间极短,功耗极低,其存贮原理可叙述如下。约瑟夫逊存贮器的每个存贮单元都有一个超导回路,超导回路中环流着恒定电流及其产生的磁通。超导回路的状态可由宏观波方程描述,但宏观波方程须满足单值条件,这样,回路中的电流和磁通都是量子化的。一个超导存贮单元(存贮1比特的基本存贮电路)包括2、3个结组成的约瑟夫逊开关电路、超导回路及其联结线路。当从联结线路接受“写”脉冲时,约瑟夫逊门跃迁至电压状态,并为写信息打开超导回路。若另一联结线路上加了电流,从而产生磁场,则回路中产生了量子化的磁通,即写进了“1”;否则,回路中没有磁通,即写进了“0”。由于单个的磁通量子(Φ0)很小(2.07×10-5韦伯),约瑟夫逊存贮单元中存贮的能量(Es)也很小。Es=Φ02/L,大约是10-13焦耳,其中L是超导回路的感应系数,一般为10微微亨。和半导体存贮单元的存贮能相比,Es要小得多,只有103~104分之一。设计约瑟夫逊存贮电路的主要问题是如何读出能量这么小的存贮信息。

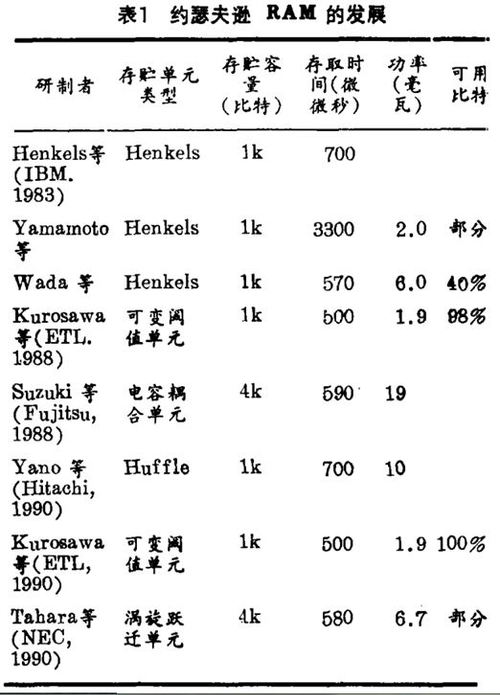

表1归约了迄今开发的约瑟夫逊RAM,从中可见,1973年,IBM的W. H. 亨凯斯及其同事首先提出并研究了一种存贮单元。这种存贮单元带有磁耦合的读取门用以读出存贮在超导回路中的磁通。由于带有读取门,这种类型的存贮单元个头大结构复杂。除读取功能外,存取单元还需一个逻辑门以便二维布线构成存贮阵列。这一要求加上读取不利使得约瑟夫逊存贮器件的设计和制作更加困难。使用这种存贮单元,日本的NTT和NEC的研究组制作了一个约1k比特的RAM芯片。最早的两个RAM芯片是采用铅合金工艺和铌边界结工艺制作的,其中结是由渐薄铌薄膜边界做成的。由于读取门和写门的容限太小,可用的比特不多。后来,NEC使用亨凯斯单元制作了一个1k比特的RAM,采用的是铌结工艺,存贮测试表明,可用的比特约占40%。这表明,为了使约瑟夫逊RAM中的单元都好使,需要新的存贮电路设计方法。最近,我们和ETL的同事们,成功地开发并展示了一个1k比特的约瑟夫逊RAM芯片,它的所有位都好使。该存贮单元和电路的设计采用了一种新方法——可变阈值存贮单元方法。

可变阈值存贮单元不像其它类型存贮单元那样使用磁耦合的读取门电路,而是采用了一种独特的读取技术,因而结构简单,工作稳定。磁耦合读取门读取的是超导回路中环流电流产生的磁场。由于存贮的磁通量太小,很难可靠地读出。而我们研制的新型存贮单元,利用其自身的阈值特性,可直接读出环流电流。以前人们害怕刷新电路庞大复杂而没有尝试这一方法。不过,我们已设计了一个非常简单的不破坏读出的反馈电路,实际表明该方法是可行的。由于存贮单元中去掉了读取门,现在的存贮单元只有原来的一半大,这样,无论在存取时间上还是在容量上都提高了RAM芯片的性能,而且也提高了存贮单元制作工艺的容限。于是,我们用铌/氧化铝/铌结工艺制成了工作良好的RAM芯片,结的边界宽度是3微米,存贮单元本身的面积是72×30微米2。1024个存贮单元和1028个逻辑门可以集成在3.7亳米见方的芯片上。存取时间是500微微秒,功耗1.9毫瓦。

约瑟夫逊计算机ETL · JC1

为了证明约瑟夫逊计算机系统的可行性,ETL(日本的电子综合研究所)设计制作了一台由多个芯片组成的约瑟夫逊计算机,取名ETL-JC1(电子综合研究所的约瑟夫逊计算机1号),它是80年代早期就开始的日本通产省研究项目的成果,采用的是ETL开发的技术。ETL自80年代早期就一直从事约瑟逊计算机技术的开发,开发出的铌和氮化铌约瑟夫逊结集成工艺已能制作出可靠的约瑟夫逊大规模集成芯片。逻辑电路,包括组合逻辑电路和时序逻辑电路,已可由4JL的直接耦合门做成。使用新型的可变阈值的约瑟夫逊RAM存贮单元,已可做成1k比特的RAM芯片,并使用一种单面双结的SQUID类型ROM单元,做成了1k比特的ROM芯片,其中存有10位长指令码写的128步的程序。

ETL-JC1是一个4位微型计算机,由4个约瑟夫逊大规模集成芯片组成:一个寄存器和算/逻部件(RALU),—个时序控制部件(SQCT),一个指令ROM部件(IROU)和一个数据RAM部件(DRAU)。芯片都是按照3-μ设计规则采用铌/氧化铝/铌结工艺制作的。IROU存贮程序。指令长度是10位,从ROM芯片读出后在RALU中译码。RALU执行算术和逻辑运算,结果存于DARU中。SQCU控制程序的时序。所有的电路均由一个直流电源供电。这是一个单极双面的电源,它也用作ETL-JC1的时钟。

组装ETL-JC1时,4个大规模集成芯片相联在印刷电路板上,各芯片通过铝线焊接到24亳米见方的芯片托架上,印刷电路板有68针的槽用以固定托架。印刷电路板下方有一塑料管,一头连着印刷电路板,另一头在做实验时浸在液氮里。由于约琴夫逊电路对磁场很敏感,因而芯片裹了6层μ金属(一种高磁导率,低浸透率的镍金属)的保护层以隔绝地球磁场和杂质磁场。另外,装配车间也一定要用非磁性材料建造。

按这种方式组装好所有的芯片后,制成的计算机成功地执行了IROU中的测试程序,表明计算机的功能正常。程序中包括全部27种指令,如算术/逻辑功能,条件转移,无条件转移,子程序调用/返回,RAM的读/写运算等。需要说明的是,在存贮器存取过程中,成功地连接了逻辑芯片和存贮器芯片,使它们成为一体地工作,这还是开天辟地的头一次。根据门延迟时间和存贮器存取时间的测试值进行的计算机逻辑模拟表明,单CPU的该系统,运算速度可达109指令/秒。

表2对ETL-JC1的RALU芯片和高速硅芯片做了对比。今后,约瑟夫逊计算机技术的发展趋势是着重开发约瑟夫逊大规模集成工艺,因为和高速硅芯片的工艺水平相比,约瑟夫逊的还处于落后状态。

[Endeavour,New Series,1991年15卷2期]